近日,南京邮电大学集成电路科学与工程学院(产教融合学院)张吉良教授团队2项研究成果分别被芯片体系架构领域ISCA、集成电路设计自动化领域DAC录用。至此,南邮集成电路学科实现在器件领域IEDM、设计领域ISSCC、架构领域ISCA、EDA领域DAC顶级会议录用全覆盖。

ISCA(International Symposium on Computer Architecture)即国际计算机体系结构研讨会,是计算机体系结构领域历史最悠久、影响力最广的顶级会议,由ACM SIGARCH和IEEE TCCA联合举办,被誉为体系结构领域的“奥斯卡”,芯片架构领域的许多创新性应用,源于该会议的论文的研究成果。DAC(Design Automation Conference)全称为设计自动化会议,是全球电子设计自动化(EDA)与芯片系统领域的顶级学术会议,覆盖EDA工具开发、AI/ML芯片设计、硬件安全等热点方向,是EDA领域唯一被中国计算机学会(CCF)列为A类的会议。

被第53届ISCA 2026直接录用的论文L-PCN: A Point Cloud Accelerator Exploiting Spatial Locality through Octree-based Islandization,第一作者为南邮集成电路科学与工程学院(产教融合学院)高一鸣博士,张吉良教授为通讯作者,合作者包括南邮计算机学院、软件学院、网络空间安全学院尹捷明教授,佛罗里达大学Herman Lam教授等。这是南邮首次在体系架构领域顶级会议上发表研究成果,也是江苏省首篇以第一单位发表的ISCA论文。

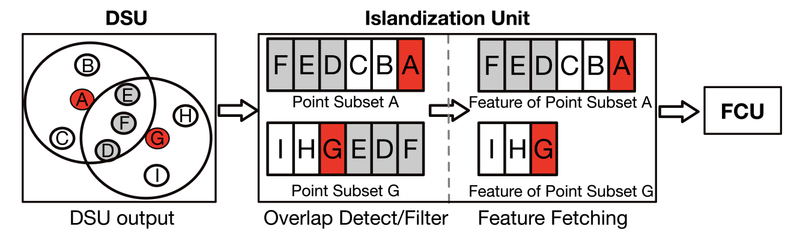

当前,大多数点云加速器侧重于开发专用的特征图收集单元,并采用NPU执行特征计算。由于点云神经网络中特征图之间存在大量重复点,导致点云加速器的NPU工作负载中存在大量重复访存和计算。研究团队借鉴图神经网络(GCN)加速器设计中跨特征图数据复用的思想,提出一种软硬件协同设计方法(L-PCN)来开发点云网络的空间局部性:软件上提出“岛屿化步骤”,可为点云模型带来最高93.8%的访存降低和最高80.6%的计算降低;硬件上设计“岛屿化单元”并自然集成到现有的点云加速器中,可额外提供最高3.2倍的加速。该工作在速度与精度保留方面均优于现有的点云特征计算优化方法。

岛屿化单元功能事例,在特征图收集单元之后,通过卷积结果复用为和特征计算单元规避重复的访存和计算

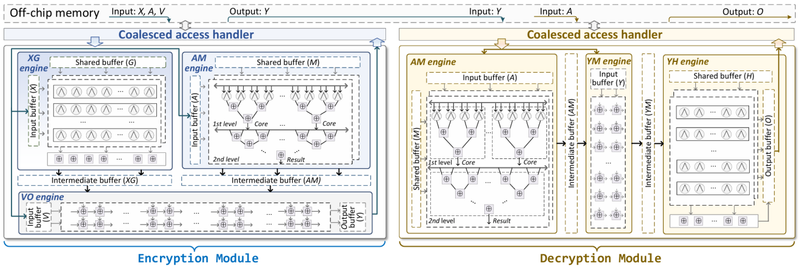

被第63届DAC 2026录用的论文Leveraging AI-Inspired Hardware Architecture to Enhance LPN Acceleration in Post-Quantum Cryptography,第一作者是南邮集成电路科学与工程学院(产教融合学院)高迎雪副教授,张吉良教授为通讯作者。后量子密码(PQC)中的LPN(Learning Parity with Noise)因结构简洁、安全性强,被视为构建高效密码系统的理想基元。但现有LPN加速器多聚焦于局部计算优化,忽视整体执行流程与数据传输瓶颈,导致硬件利用率和系统吞吐量受限。受AI加速器架构启发,研究团队首次提出面向FPGA的LPN硬件加速架构——LHPA:采用异构计算引擎、层次化XOR归约树与流式执行机制,全面优化LPN的多阶段计算与数据传输;针对LPN中多传输、单比特的数据特征,设计了合并访问处理器与阶段级调度策略,将片外传输效率提升51.16%,显著缓解访存瓶颈、增强架构适应性。实验结果表明:在Zynq UltraScale+ FPGA上,LHPA相比现有最先进的LPN加速器(PIM-LPN)实现了52.80倍的性能提升,相比主流PQC加速器(BIKE、HQC、Kyber)提升幅度达36.69倍至247.35倍;硬件平均利用率达90.71%,访存效率最高提升47.25%。LHPA是首个在FPGA上实现高效、可配置、高吞吐LPN加速的AI启发架构,为后量子密码硬件设计开辟了新路径。

LHPA整体架构

南邮全面构建“信息材料、信息器件、信息系统、信息网络、信息应用”五位一体的大信息学科体系,聚焦集成电路领域“卡脖子”技术难题,深化产教融合,强化有组织科研,聚力在前沿方向实现原创性引领性突破,为国家集成电路产业自主可控发展和拔尖创新人才培养贡献南邮力量。

(撰稿:高一鸣、高迎雪、王海华 初审:高翔、李炳祥 编辑:王存宏 审核:张丰)