| 南邮在集成电路领域国际会议发表三篇重要论文 |

| 发布时间: 2025-06-26 浏览次数: 4148 文章来源: 集成电路科学与工程学院(产教融合学院),科学技术处 |

|

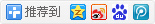

6月22日至25日,南京邮电大学尹捷明教授团队李骏、陈小柏、尹捷明老师在第62届设计自动化会议(Design Automation Conference, DAC 2025)发表题为FineRR-ZNS: Enabling Fine-Granularity Read Refreshing for ZNS SSDs的研究论文。DAC是中国计算机学会推荐的A类国际学术会议,由美国计算机协会(ACM)和电气与电子工程师协会(IEEE)联合主办,是电子设计自动化(EDA)领域的顶级会议。该研究针对分区命名空间固态硬盘(ZNS SSD)中区域级读刷新机制导致的数据迁移开销过大的问题,提出了一种细粒度读刷新机制FineRR-ZNS。该方案采用主机控制的块级选择性刷新策略,通过元数据重映射技术实现精准刷新区块定位,并设计了区域重构方法,在确保数据完整性的同时优先访问重映射数据,直至对应数据块需要再次刷新。实验结果表明,该机制可平均提升I/O吞吐率28.2%,同时提高41.8%的存储空间利用率。

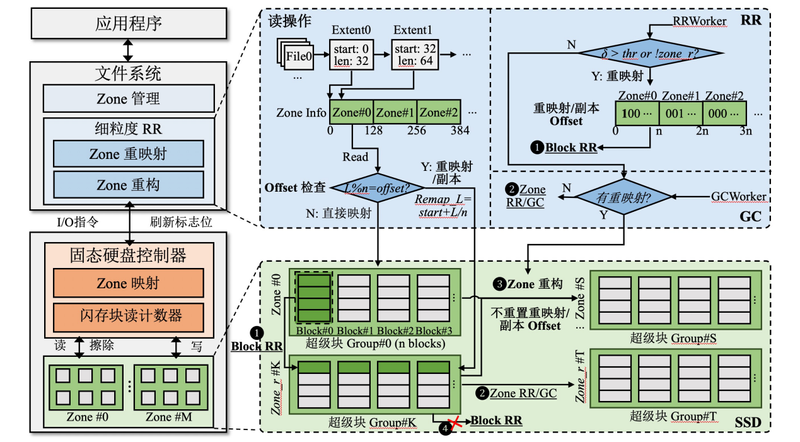

机制概述 6月8日至12日,南邮郭宇锋教授团队在第45届VLSI工艺与电路研讨会(45th Symposium on VLSI Technology and Circuits,VLSI 2025)发表创新研究成果,实现了南京邮电大学在该顶级国际会议上的首次突破。该成果题为A 24-MHz Crystal Oscillator with 6.9-μs Startup Time and 2% Injection-ΔF Tolerance Using Phase-Interpolator-Assisted Synchronized Injection,由集成电路科学与工程学院博士研究生王鑫担任第一作者,王子轩教授、蔡志匡教授、麦沛然教授共同担任通讯作者。研究聚焦于物联网设备中时钟系统启动缓慢的行业痛点,创新性提出基于相位插值器的同步注入技术。通过高效相位同步的注入机制,该技术显著缩短了时钟源的启动时间,为解决时钟系统启动延迟问题提供了全新思路。研究团队采用40纳米工艺完成芯片流片验证,测试数据显示:时钟源启动时间从传统技术的1.32毫秒大幅缩减至6.9微秒,优化效果达191.3倍;同时实现±2%的超大注入频率偏差容限,充分验证了该技术的高性能与高可靠性。这一成果为物联网设备的高效运行提供了关键技术支撑,具有显著的应用价值。

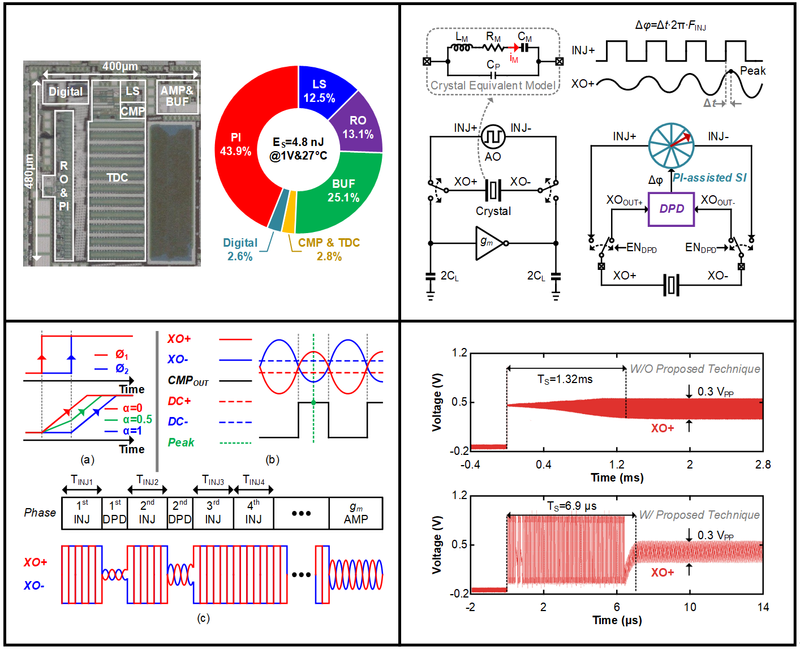

芯片技术原理 6月1日至5日,南邮郭宇锋教授团队在第37届国际功率半导体器件与集成电路会议(37th International Symposium on Power Semiconductor Devices and ICs, ISPSD 2025)发表创新研究成果,以第一作者陈静,通讯作者郭宇锋完成的Intelligent Design of Superjunction Devices Based on Physics-informed Neural Network被大会收录。该研究针对传统设计方案中“人在回路”的局限,提出了超结功率器件物理信息网络(SJ-PiNN)智能设计方案。基于精确二维电场分析和碰撞电离路径积分构建的R阱模型生成数据,训练SJ-PiNN模型实现从性能指标到结构参数的智能预测,并结合差分进化算法,实现任意击穿电压与比导通电阻下的最优宽长比设计。结果表明SJ-PiNN的R2预测准确率>99.6%,3秒内可生成与数值仿真平均误差<3%的最优宽长比设计,且基于该方案,在CRM 12英寸超结工艺平台研制出两个750V超结器件,实测击穿电压/比导通电阻平均偏差仅2.4%/5.1%。

研究方案 (撰稿:王子轩、姚佳飞 初审:高翔、蔡志匡 编辑:王存宏 审核:张丰) |

仙林校区地址:南京市仙林大学城文苑路9号 邮编:210023 三牌楼校区地址:南京市新模范马路66号 邮编:210003 锁金村校区地址:南京市龙蟠路177号 邮编:210042

联系电话:(86)-25-85866888 传真:(86)-25-85866999 邮箱:njupt@njupt.edu.cn

苏公网安备32011302320419号 |苏ICP备11073489号-1

苏公网安备32011302320419号 |苏ICP备11073489号-1

Copyright © Nanjing University of Posts and Telecommunications All Rights Reserved